English translation

Présentation

Le terminal que je vais vous

décrire, est une console alpha numérique de 1969, qui utilise des

lignes à retard TV comme éléments mémoire. Elle a été, à l'origine,

étudiée aux Pays-bas (chez Philips) et nous est parvenue sous la marque

RTC (branche Française de Philips composants).

En 1969, il n'y avait pas encore de circuits intégrés offrant des fonctions de mémorisation. On utilisait encore les mémoires à tores de ferrite, ou d'autres technologie comme les mémoires acoustiques à mercure, ou des mémoires à commutation de capacités.

Ce terminal d'affichage utilise un écran standard de télévision, en mode non entrelacé (312 lignes, 50 images par seconde). En réalité le tube de ce terminal était doté d'un phosphore rémanent, et d'une dalle antireflet.

L'industrie de la télévision utilisait pour le décodage de la couleur de nouvelles lignes à retard de 64 uS (à réflexions multiples). [vous savez, le séquentiel couleur de notre SECAM: Rouge/Bleu/Rouge/B/R/B...]. La bande passante de ces lignes à retard était de 4.5 MHz. On cherchait à afficher 80 caractères par rangée de texte. La zone d'affichage correspond classiquement à 52 uS, par rapport au 64 uS d'une ligne TV. (12 uS sont réservées au retour du spot vers la prochaine ligne.)

Le codage ASCII se faisait sur 6 bits. Il fallait donc 80 car x 6 bits =480 bits en 52 uS. Soit une fréquence double que celle offerte par les lignes à retard. Il faudra donc 2 jeux de lignes à retard en parallèle!

L'étude de cette machine montrera, qu'il faudra 32 lignes à retard pour afficher 16 rangées de 80 caractères.

La machine comporte:

En 1969, il n'y avait pas encore de circuits intégrés offrant des fonctions de mémorisation. On utilisait encore les mémoires à tores de ferrite, ou d'autres technologie comme les mémoires acoustiques à mercure, ou des mémoires à commutation de capacités.

Ce terminal d'affichage utilise un écran standard de télévision, en mode non entrelacé (312 lignes, 50 images par seconde). En réalité le tube de ce terminal était doté d'un phosphore rémanent, et d'une dalle antireflet.

L'industrie de la télévision utilisait pour le décodage de la couleur de nouvelles lignes à retard de 64 uS (à réflexions multiples). [vous savez, le séquentiel couleur de notre SECAM: Rouge/Bleu/Rouge/B/R/B...]. La bande passante de ces lignes à retard était de 4.5 MHz. On cherchait à afficher 80 caractères par rangée de texte. La zone d'affichage correspond classiquement à 52 uS, par rapport au 64 uS d'une ligne TV. (12 uS sont réservées au retour du spot vers la prochaine ligne.)

Le codage ASCII se faisait sur 6 bits. Il fallait donc 80 car x 6 bits =480 bits en 52 uS. Soit une fréquence double que celle offerte par les lignes à retard. Il faudra donc 2 jeux de lignes à retard en parallèle!

L'étude de cette machine montrera, qu'il faudra 32 lignes à retard pour afficher 16 rangées de 80 caractères.

La machine comporte:

- un clavier alphanumérique de 48 touches, et quelques touches de fonction.

- Une logique de séquencement.

- Une mémoire de 1280 mots de 6 bits (1 k octet!) donc composées de 32 lignes à retard.

- Un générateur de caractère 5x7 composé de 2 circuits intégrés FDR-116-Z1 qui fonctionneront en alterné pour des problèmes de vitesse insuffisante.

- 4 paires de roues codeuses pour définir les 4 tabulations possibles.

- Une alimentation externe (non décrite).

- Un coffret 24".

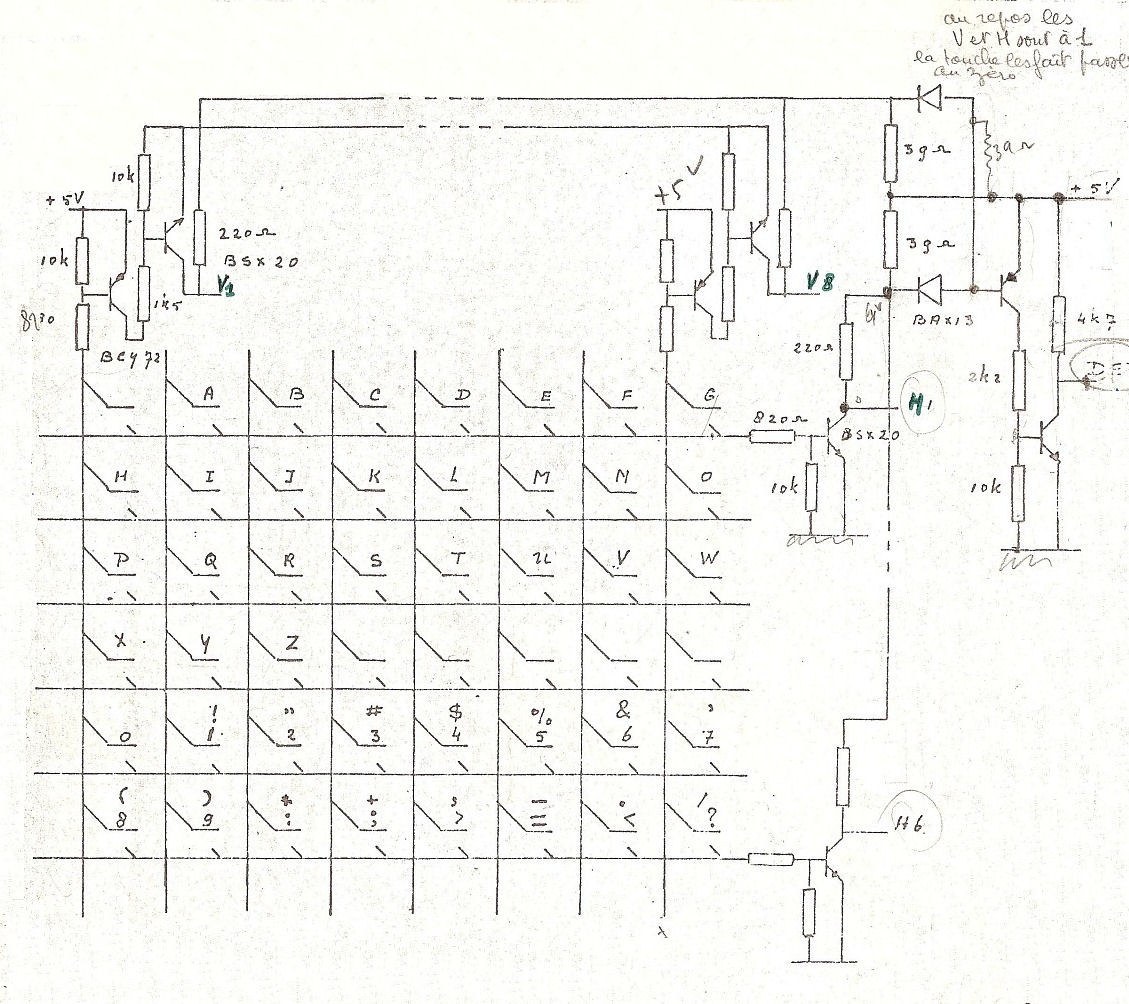

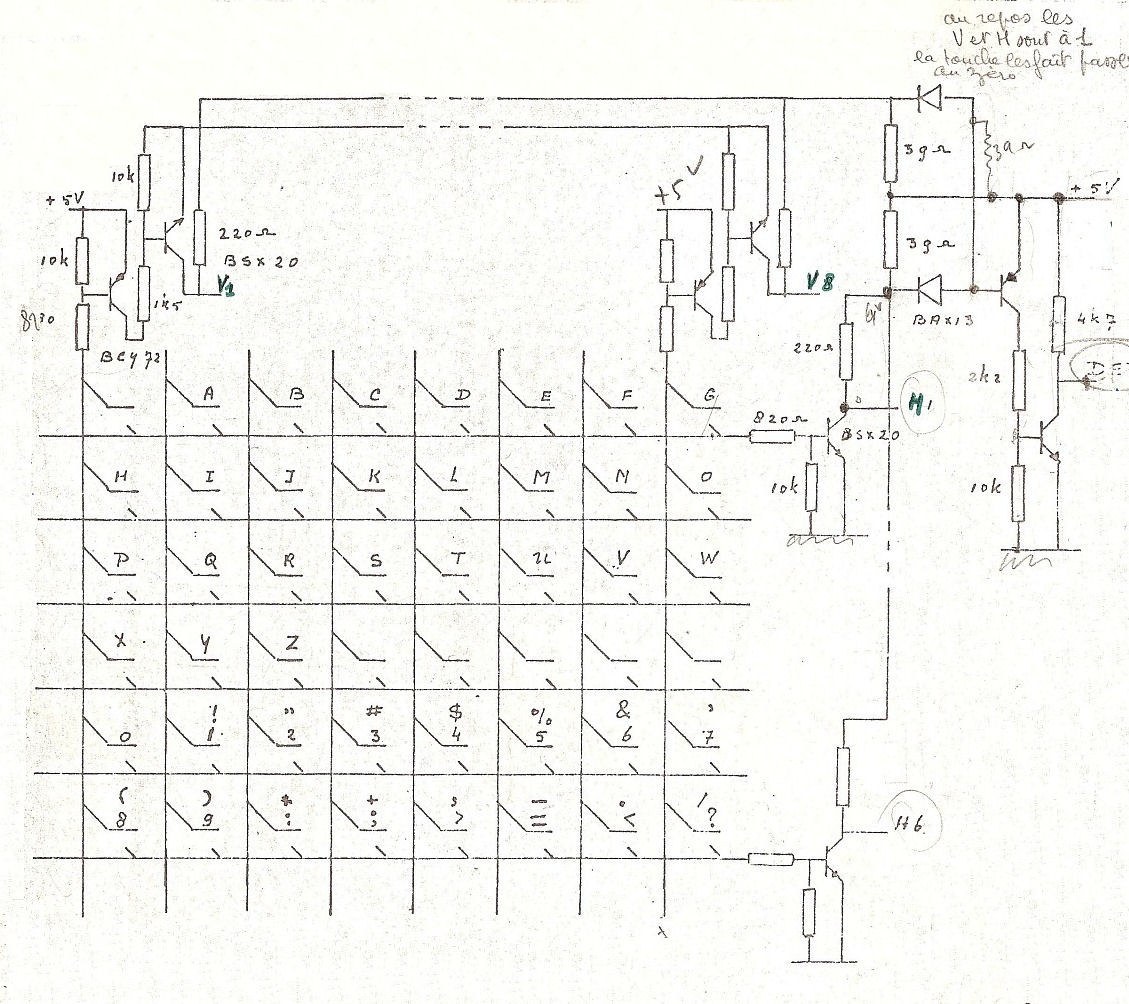

Etude du clavier

Le clavier est formé de 2 types de

touches:

Touches de fonction

L'anti-rebonds

L'étude des contacts électriques montre qu'il y a beaucoup de rebonds (pendant une durée d'environ 10 mS) Auparavant, on travaillait en électromécanique, et les défauts de contact n'étaient pas importants. L'électronique rapide de 1970 permettait de voir tous ces rebonds, qui introduisaient de très nombreux dysfonctionnements. Il fallait corriger cela en créant une fonction anti-rebonds. On trouvera cette fonction associée à chacun des types de touches.

On peut trouver la description complète de son fonctionnement ici: AntiRebonds.pdf (notes de l'époque... avec fautes!)

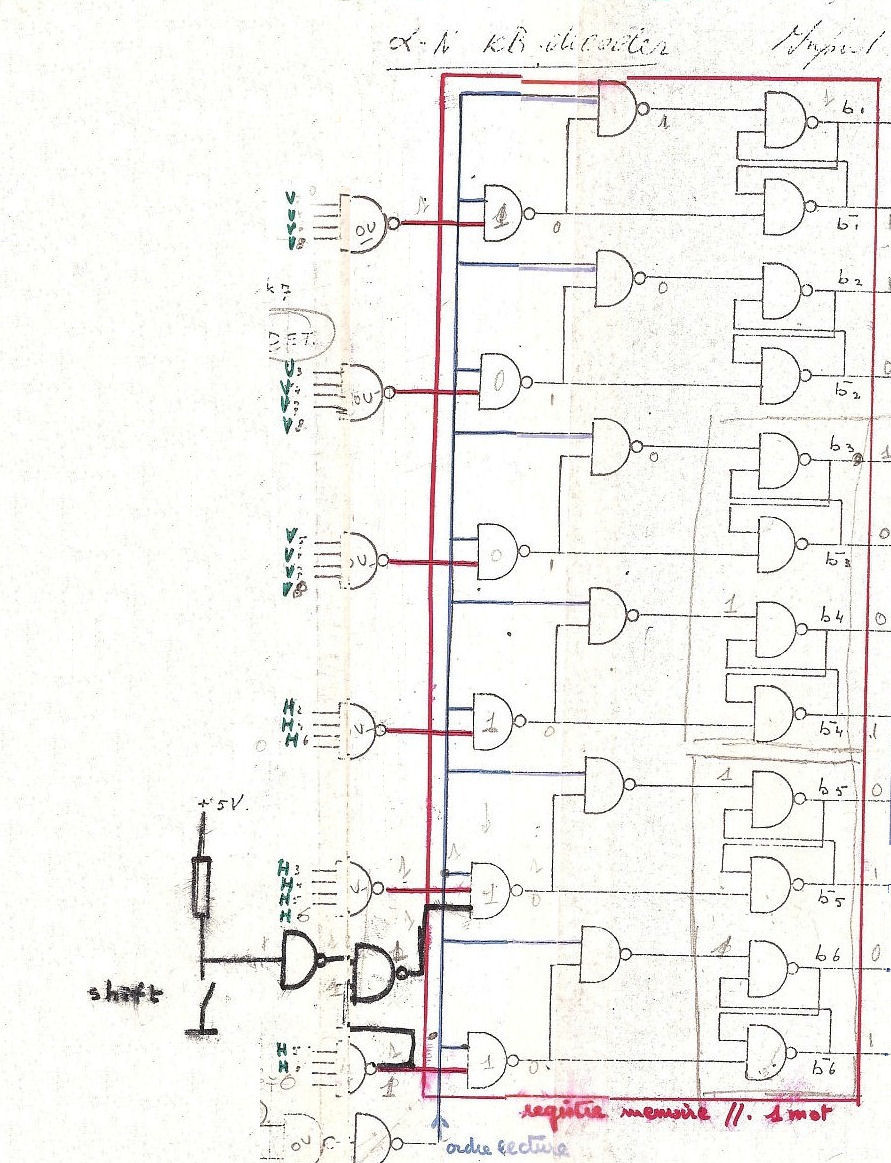

Le codage ASCII et mise en registre

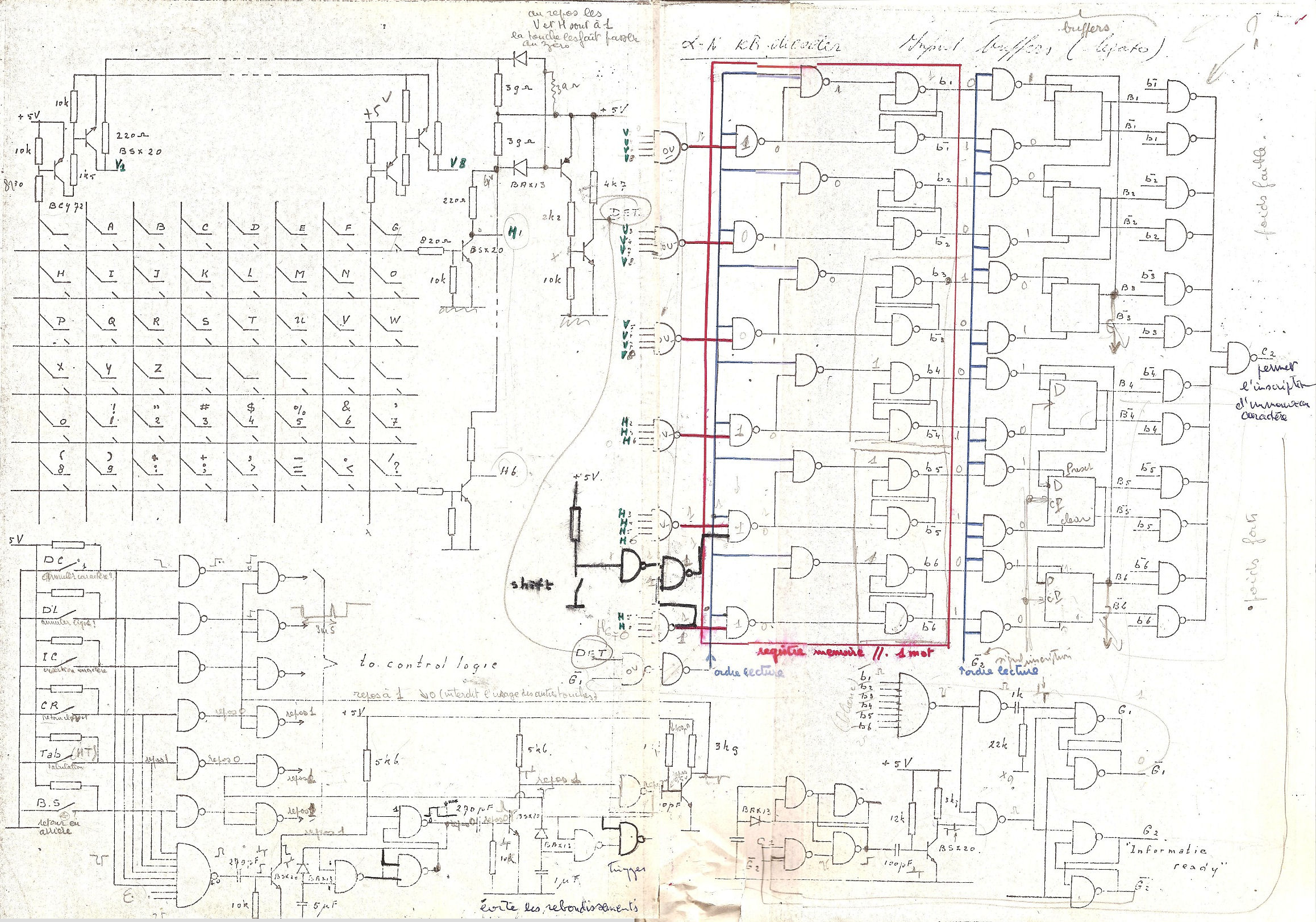

Le plan complet du clavier

- Les touches alphanumériques A..Z 0..9 et quelques signes comme ! " # $ % & ' ( ) * + - =, . ; : ? / espace qui sont disposées sur une matrice de 6x8. Une touche spéciale de shift permet d'avoir les 64 caractères définis.

Fonctionnement:

Les contacts sont fermants. A

chaque colonne est associée une paire de transistors BCY72 et BSX20.

L'élément sensible est la base du BCY72 reliée à la colonne par une 820

ohms. Au repos, cette 820 ohms est non connectée, laissant la base du

PNP alimentée par du 5 volts: il est bloqué.

De même les lignes horizontales sont reliées à la base d'un NPN. Au repos, cette base non alimentée bloque le transistor.

Un contact dans une touche, alimentera un transistor colonne (bcy72) et un transistor ligne (bsx20).

Les autres transistors ne bougerons pas!

Ainsi la logique devra surveiller les niveaux de sortie des 8 paires du haut (V1 à V8) et les 6 transistors de droite (H1 à H6)

Le circuit de droite, avec les diodes, permet de détecter l'appui d'une touche (DET) et démarrera le circuit anti-rebonds.

De même les lignes horizontales sont reliées à la base d'un NPN. Au repos, cette base non alimentée bloque le transistor.

Un contact dans une touche, alimentera un transistor colonne (bcy72) et un transistor ligne (bsx20).

Les autres transistors ne bougerons pas!

Ainsi la logique devra surveiller les niveaux de sortie des 8 paires du haut (V1 à V8) et les 6 transistors de droite (H1 à H6)

Le circuit de droite, avec les diodes, permet de détecter l'appui d'une touche (DET) et démarrera le circuit anti-rebonds.

- Des touches de fonctions au concept nouveau pour l'époque: suppression, insertion d'un caractère, suppression, insertion d'une rangées de caractères, retour à la ligne et back space. N'oubliez pas que l'on ne connaissait que les machines à écrire ou les téléimprimeurs (Teletypes) Les secrétaires devaient mettre de la peinture pour effacer un caractère!

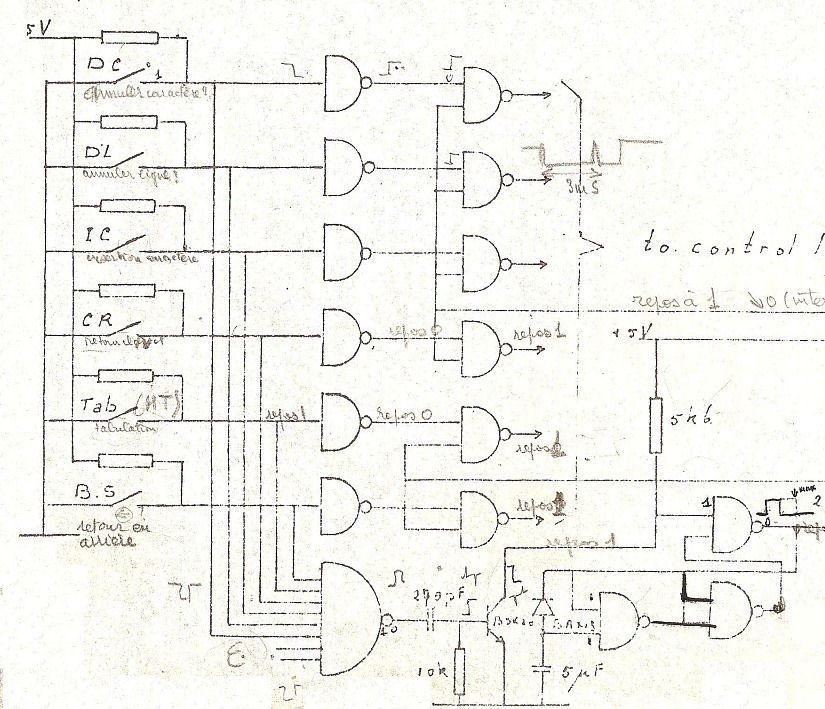

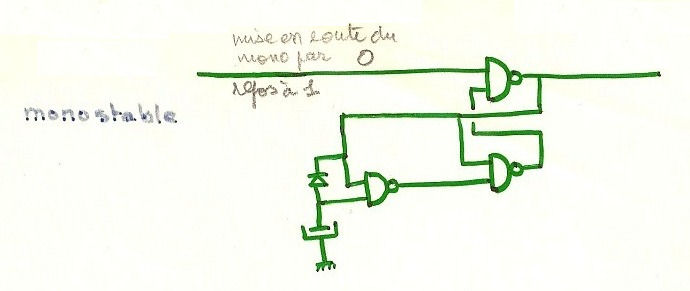

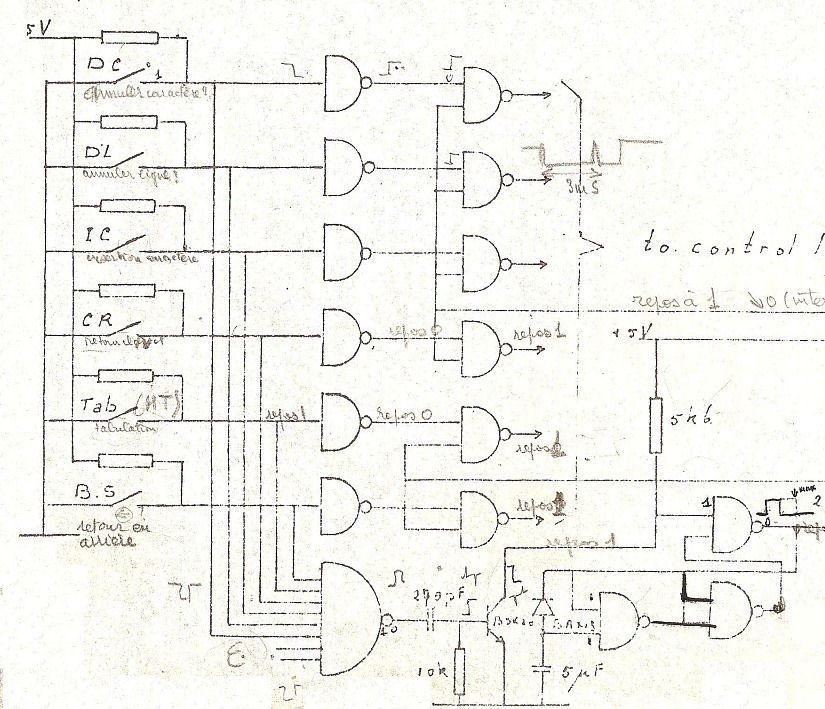

Touches de fonction

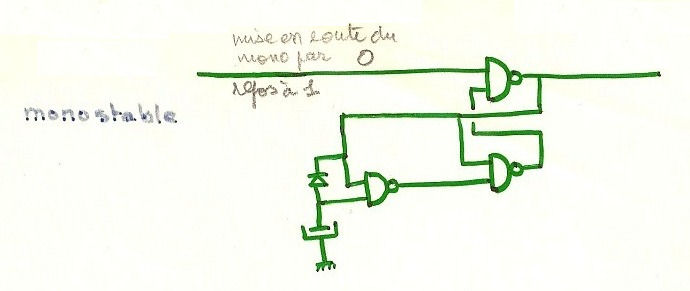

Le circuit n'est pas

matriciel. Chaque touche a son circuit. Le NAND8 fait office de OR et

détecte qu'une touche a été appuyée. Il enclenchera un circuit

anti-rebonds. (qui sera suivi par une série de retards)

L'anti-rebonds

L'étude des contacts électriques montre qu'il y a beaucoup de rebonds (pendant une durée d'environ 10 mS) Auparavant, on travaillait en électromécanique, et les défauts de contact n'étaient pas importants. L'électronique rapide de 1970 permettait de voir tous ces rebonds, qui introduisaient de très nombreux dysfonctionnements. Il fallait corriger cela en créant une fonction anti-rebonds. On trouvera cette fonction associée à chacun des types de touches.

On peut trouver la description complète de son fonctionnement ici: AntiRebonds.pdf (notes de l'époque... avec fautes!)

Le codage ASCII et mise en registre

Le plan complet du clavier

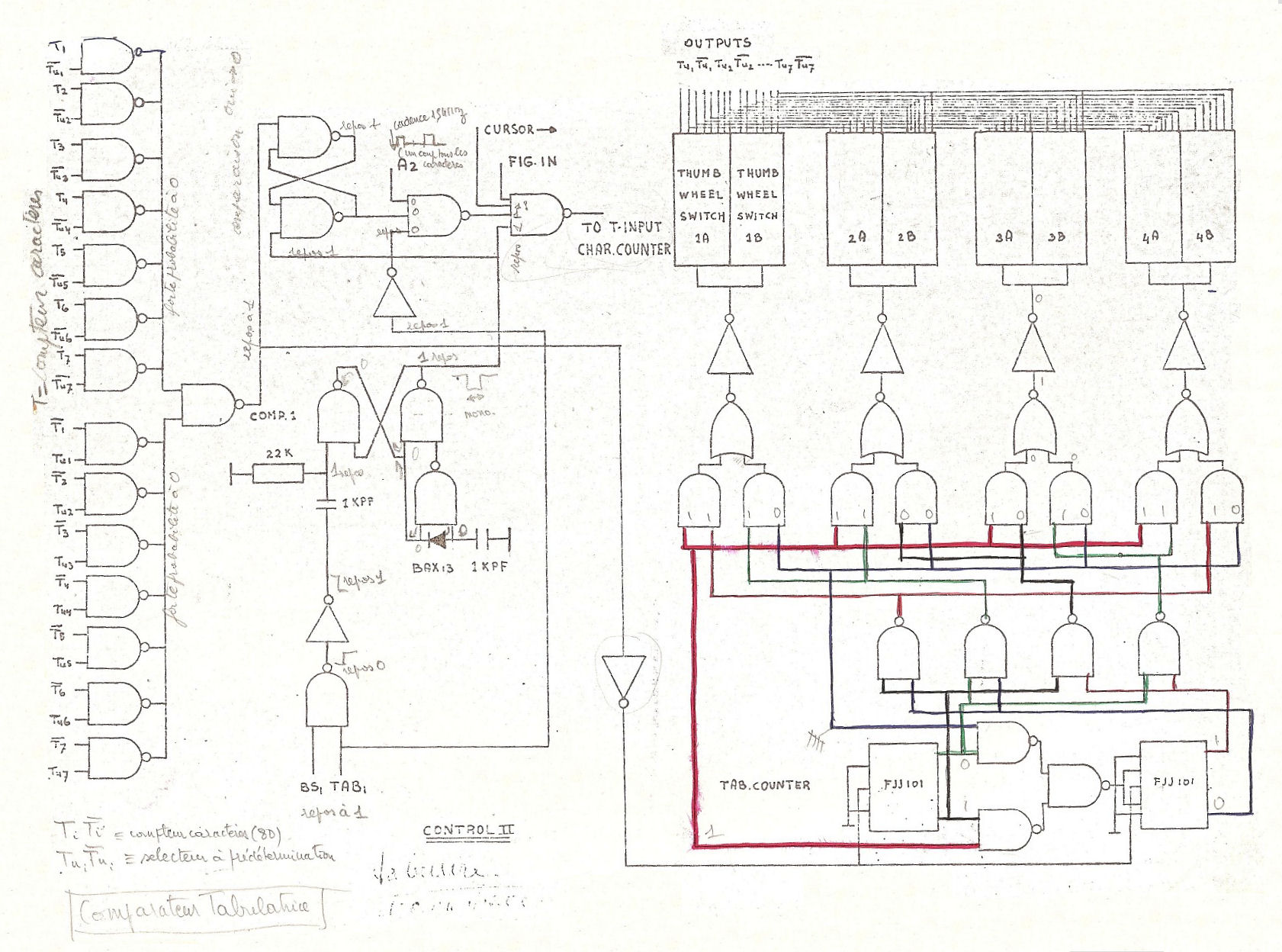

La tabulation et quelques circuits de contrôle

On voit ci-dessus, à gauche, un

compteur 2 bits pour sélectionner une des 4 paires de codeurs décimaux

pour la tabulation.

Sur la gauche un comparateur avec le compteur caractères qui enclenche une série d'avance du curseur jusqu'à atteindre la bonne position.

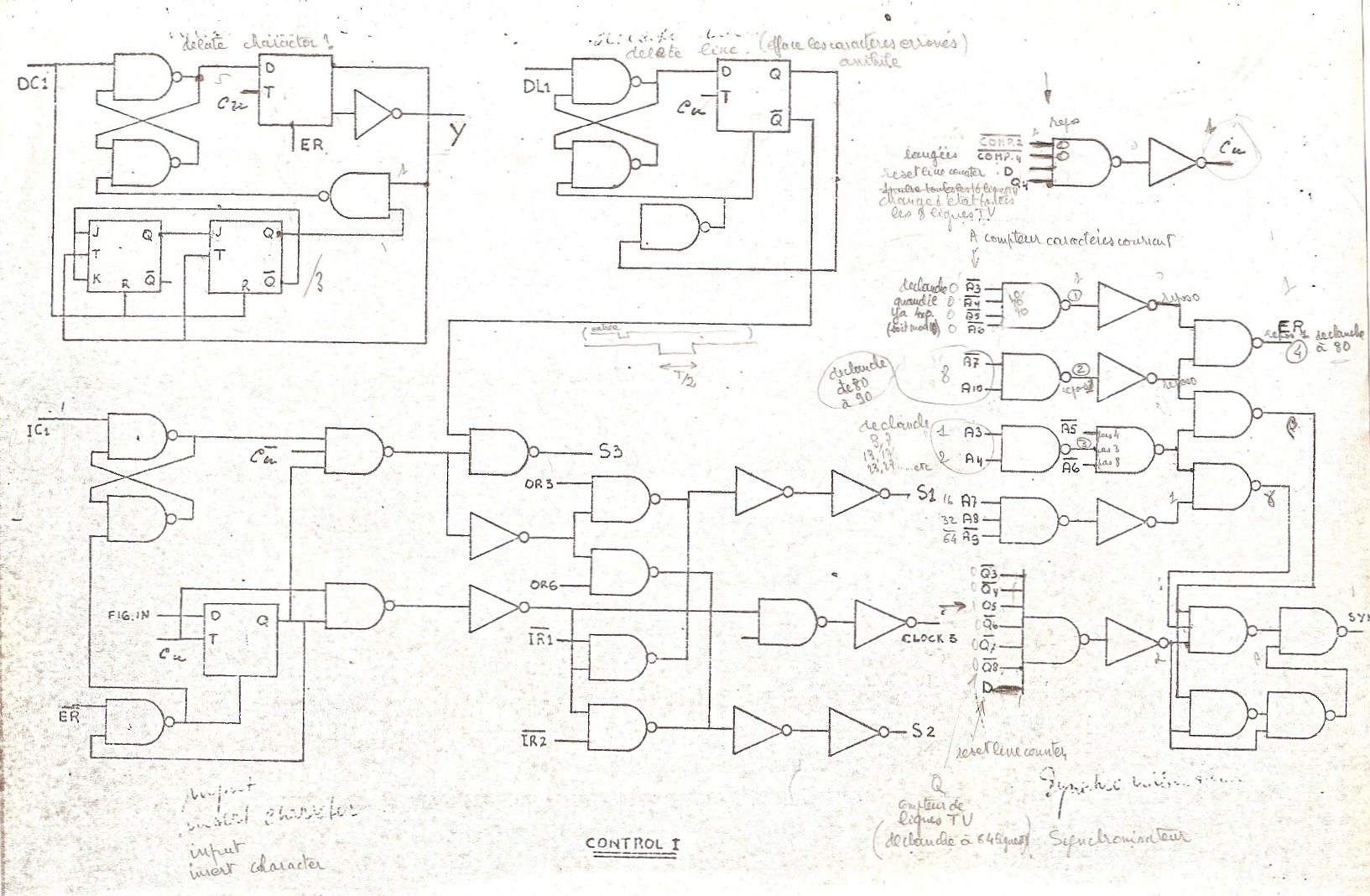

Et ci-dessous, les signaux de contrôle pour insertion/suppression de caractères ou suppression de rangées de caractères:

Sur la gauche un comparateur avec le compteur caractères qui enclenche une série d'avance du curseur jusqu'à atteindre la bonne position.

Et ci-dessous, les signaux de contrôle pour insertion/suppression de caractères ou suppression de rangées de caractères:

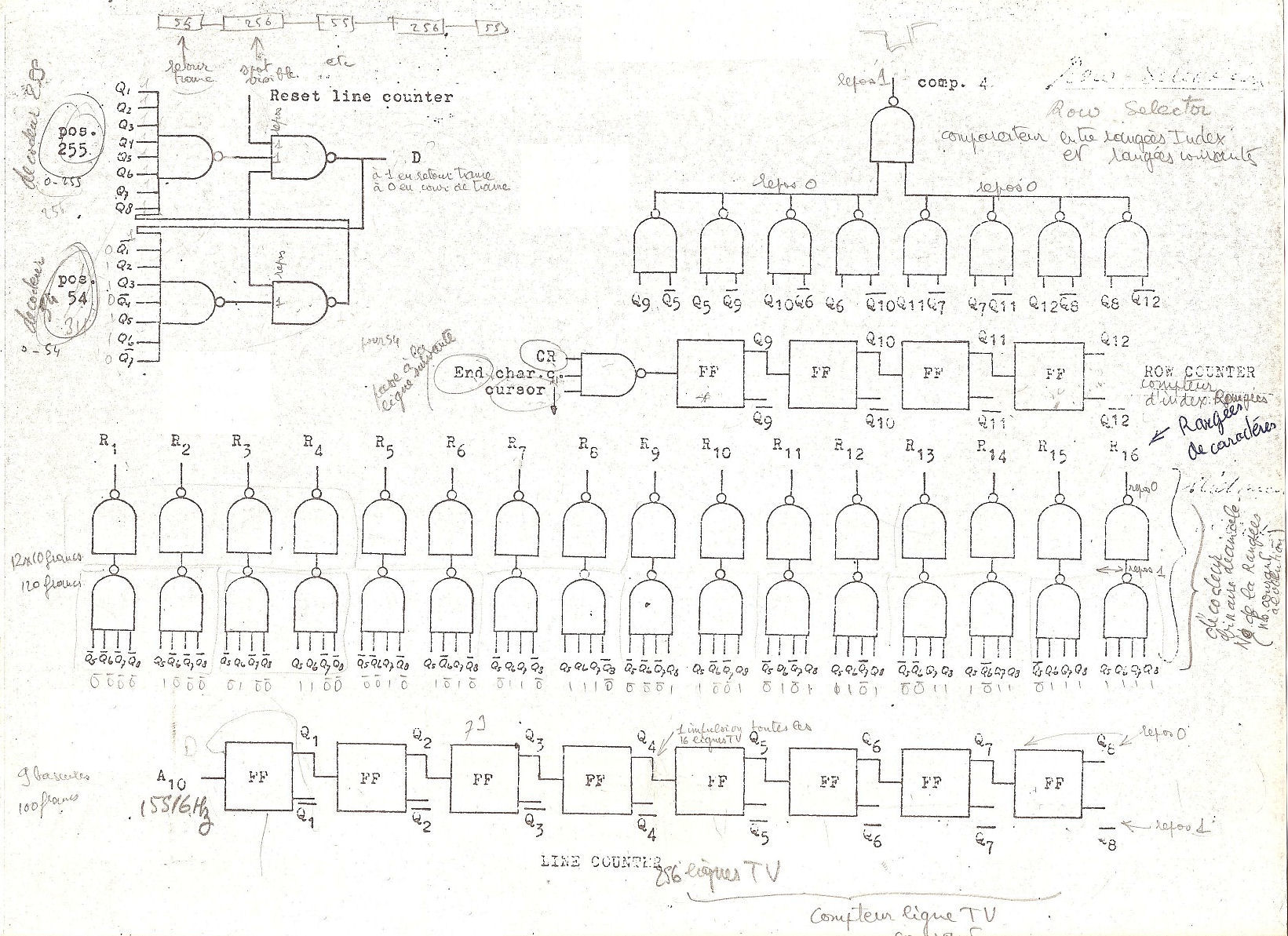

Génération des timings et gestion du curseur

En

horizontal

A partir d'un quartz de 13.9643 MHz on va obtenir toutes les fréquences utiles dans une chaîne de visualisation. On a vu qu'il fallait lire 80 codes ascii en 52 us (partie visible d'une ligne), ce qui veut dire qu'une complète (visible +retour du spot) de 64uS réclamera un comptage à 100 [52/80 x64]

Ces raisons expliquent pourquoi une pré division par 3, puis par3 (donc par 9) sera suivi par un diviseur par 100 [10 suivi de 10] pour obtenir du 15516 Hz qui correspond à la fréquence balayage ligne d'une télévision (en réalité cela devrait être 15 625 Hz)

Ainsi un compteur courant (A0 à A10) permettra de connaitre la position du spot sur l'écran:

Pour montrer le curseur sur l'écran, une logique établira la coïncidence entre le compteur courant A10..A3 et le pointeur du curseur T7..T1

La page A3 complète:

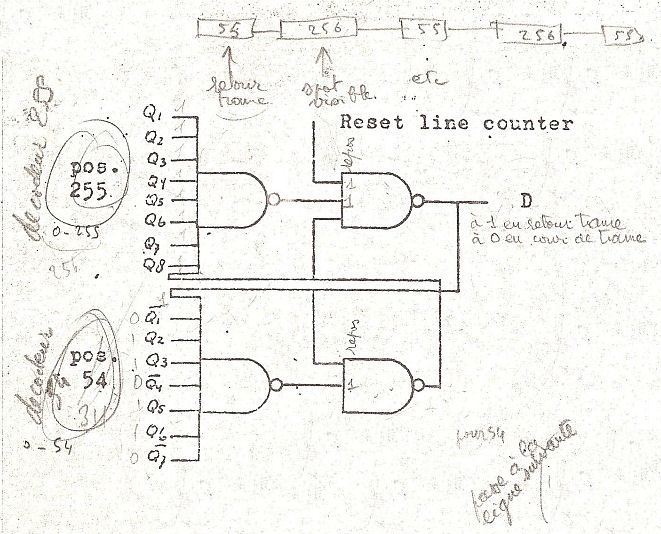

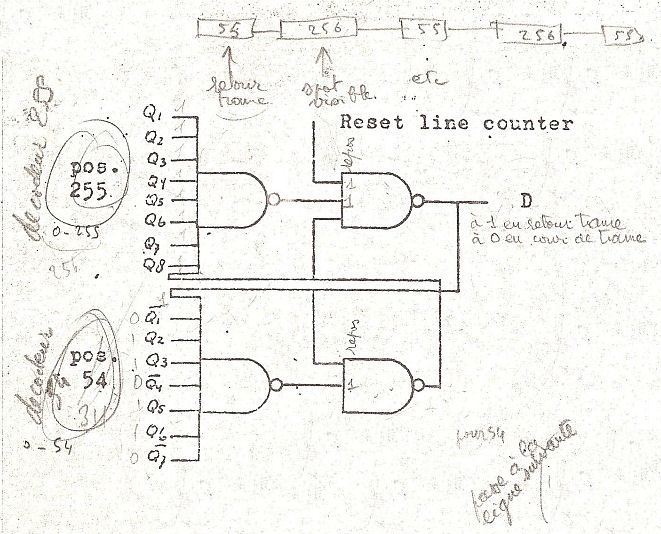

En vertical

Il nous faut une solution pour déterminer la ligne dans un caractère, et la sélection de chacune des 16 rangées correspondant à des chip select des lignes à retard.

Il faut aussi définir les 54 lignes nécessaire au retour trame du spot.

On doit aussi faire la gestion verticale du curseur.

Comme il n'y a pas de contrainte particulière concernant le retard pour la chaîne de comptage, on peut prendre de simples bascules. (On travaille à 15 625 Hz)

Compteur courant vertical Q1..Q8

Partie visible/invisible

Compteur vertical pour le curseur et génération curseur

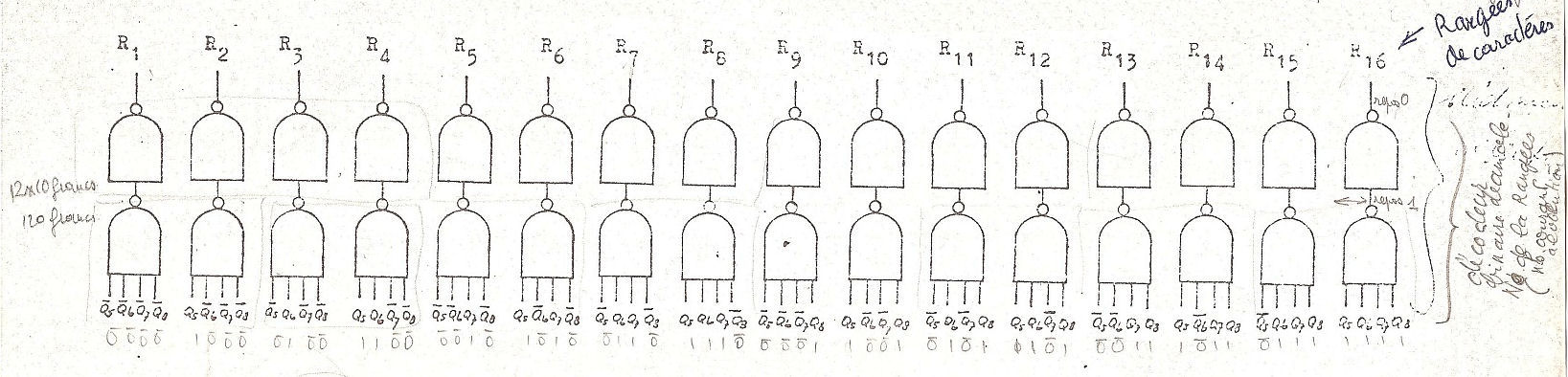

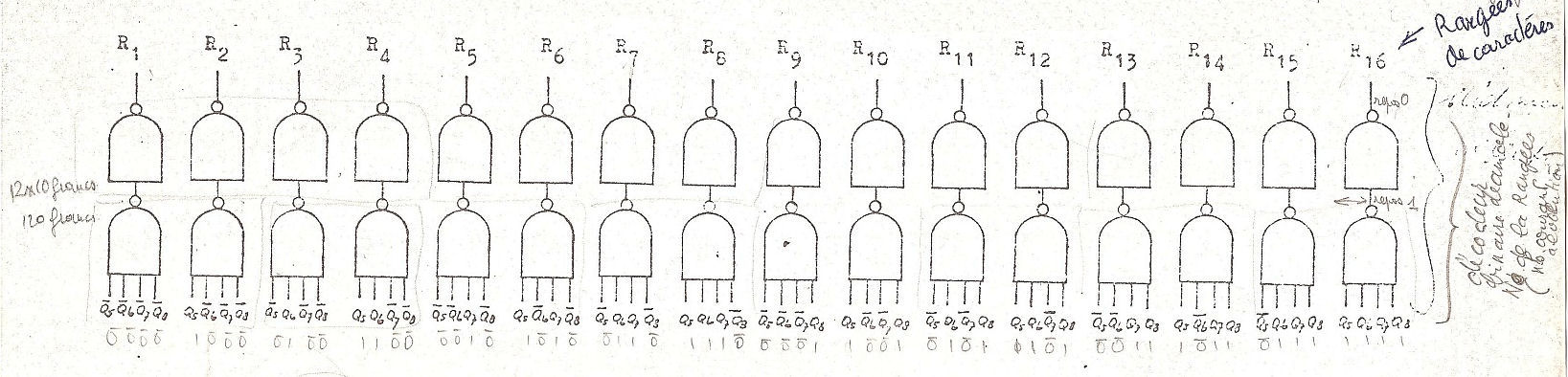

Génération des Delay Lines selects

(un simple démultiplexeur 74'154)

La page A4 complète:

A partir d'un quartz de 13.9643 MHz on va obtenir toutes les fréquences utiles dans une chaîne de visualisation. On a vu qu'il fallait lire 80 codes ascii en 52 us (partie visible d'une ligne), ce qui veut dire qu'une complète (visible +retour du spot) de 64uS réclamera un comptage à 100 [52/80 x64]

Ces raisons expliquent pourquoi une pré division par 3, puis par3 (donc par 9) sera suivi par un diviseur par 100 [10 suivi de 10] pour obtenir du 15516 Hz qui correspond à la fréquence balayage ligne d'une télévision (en réalité cela devrait être 15 625 Hz)

Ainsi un compteur courant (A0 à A10) permettra de connaitre la position du spot sur l'écran:

- A2..A0 indiquera la position horizontale du spot dans un caractère

- A10..A3 indiquera pour les 80 premiers états la position d'un caractère sur une rangée; les 20 suivantes correspondront au retour du spot horizontal.

- vers la droite -> décomptage

- vers la gauche -> comptage

Pour montrer le curseur sur l'écran, une logique établira la coïncidence entre le compteur courant A10..A3 et le pointeur du curseur T7..T1

La page A3 complète:

En vertical

Il nous faut une solution pour déterminer la ligne dans un caractère, et la sélection de chacune des 16 rangées correspondant à des chip select des lignes à retard.

Il faut aussi définir les 54 lignes nécessaire au retour trame du spot.

On doit aussi faire la gestion verticale du curseur.

Comme il n'y a pas de contrainte particulière concernant le retard pour la chaîne de comptage, on peut prendre de simples bascules. (On travaille à 15 625 Hz)

Compteur courant vertical Q1..Q8

Partie visible/invisible

Compteur vertical pour le curseur et génération curseur

Génération des Delay Lines selects

(un simple démultiplexeur 74'154)

La page A4 complète:

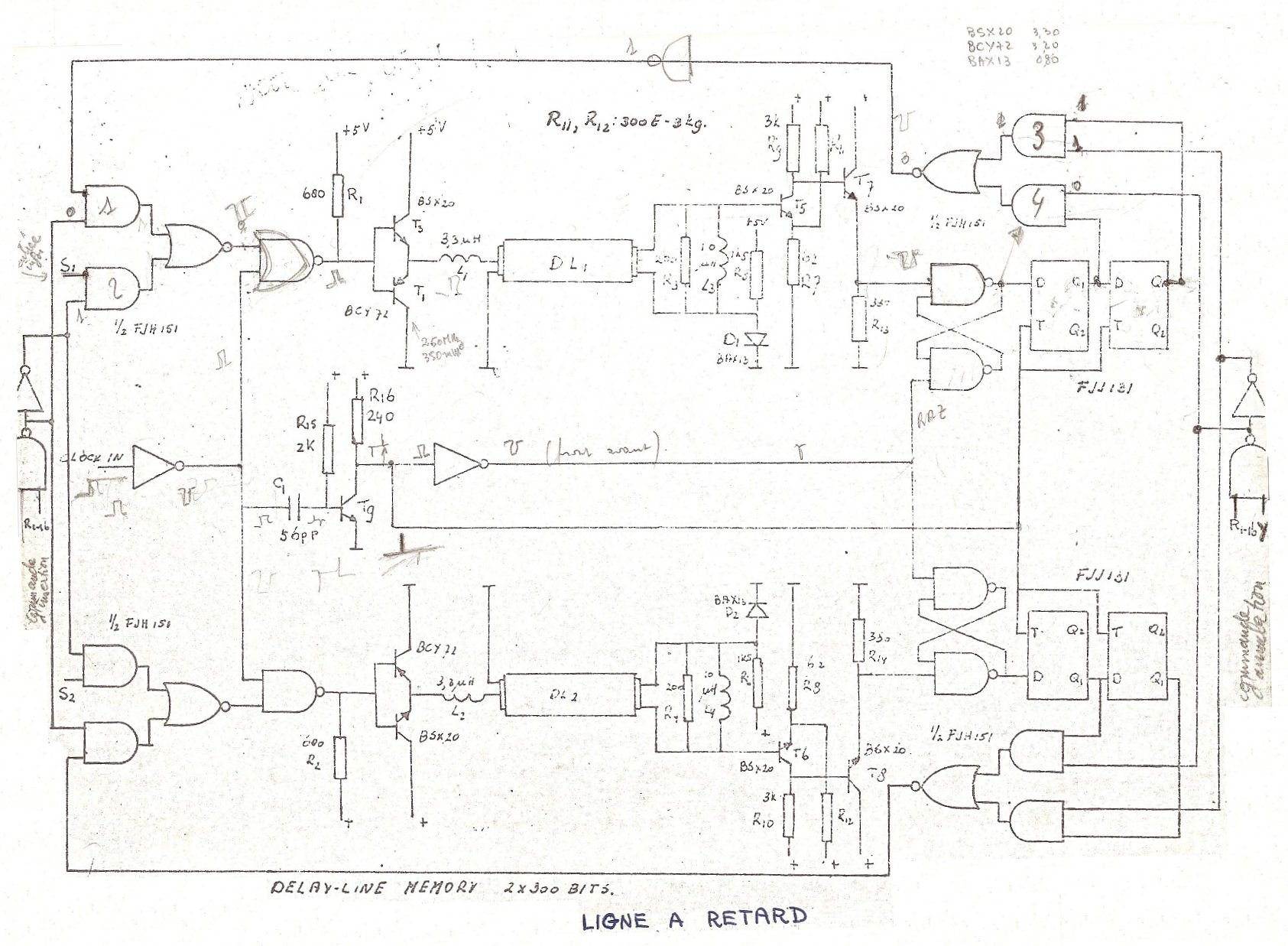

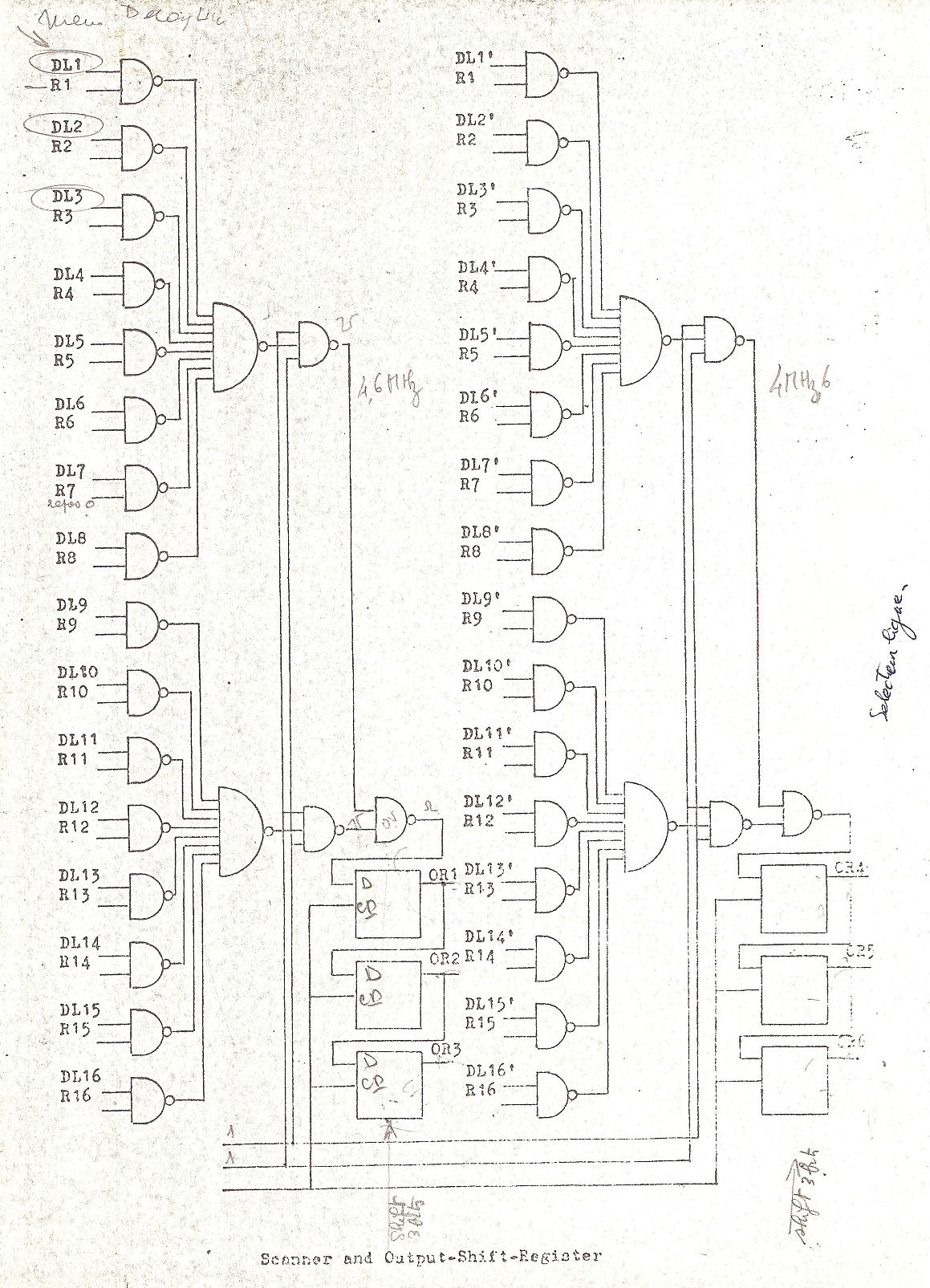

La mémoire à lignes à retard

Nous avons vu qu'il fallait 2 lignes à retard en alternance, car une ligne ne pouvait mémoriser que 300 bits. Nous allons donc trouver une circuiterie de démultiplexage en entrée et une de multiplexage en sortie.

En sortie, nous avons aussi 2 bascules de décalage et un sélecteur permettant les fonctions d'insertion/suppression de caractère. (On allonge ou on raccourcit la longueur de shift)

Ensuite il faut lire les 32 lignes à retard et générer le code ascii (court) qui sera présenté aux 2 générateurs de caractères.

Ce montage est équivalent à 2x2 74'151 suivi par un 74'174. Les lignes à retard se situent mentalement sur la gauche.

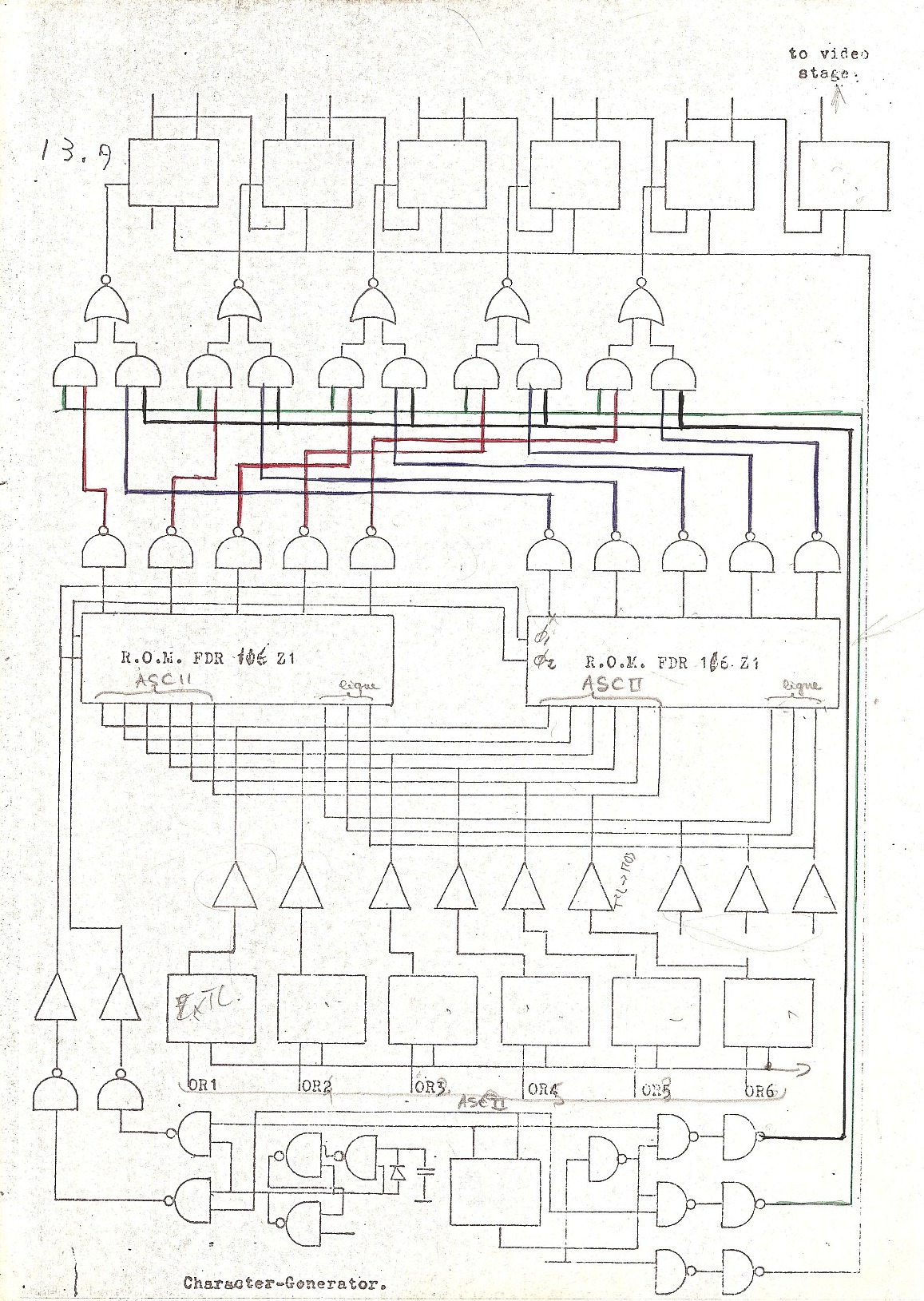

La génération des caractères

Il faut maintenant arriver au but de la machine: générer un signal vidéo pour être envoyé sur un moniteur de télévision. Il faut donc générer le graphisme. On dispose pour cela de circuit LSI spécialisé, le FDR-116-Z1.

Il faut présenter à ce genre de circuit le code ascii sur 6 bits et le numéro de la ligne TV du caractère en cour d'affichage. (donc Q4..Q1 puisque il y a 16 rangées de caractères en 256 lignes visibles)

Ne pas oublier que pour des raisons de vitesse, il faut 2 GC en parallèle... Le schéma suivant va décrire (de bas en haut):

- un peu de glue logic pour générer les 2 phases Phi1 et Phi2 du MOS.

- Un registre pour mémoriser le code ascii

- une rangée de buffer TTL -> MOS

- 2 GC

- Une rangée de buffers MOS -> TTL

- une rangée de multiplexeur 6x1 bit

- le registre // série classique qui sera excité au rythme des pixels. (la plus haute fréquence du compteur courant)

Part list

Cette machine utilise:

- 254 circuits intégrés

- 186 transistors

- 50 diodes

- 396 résistances

- 32 lignes à retard

- 40 condensateurs

- 2 LSI MOS

- etc.

L'évolution de cette machine

En 1970, sont apparus les

premiers circuits intégrés de mémoire. L'industrie a commencé par

utiliser des registres à décalage, car on savait que les registres

(shifts) offrent une plus grande intégration que la mémoire RAM (à

accès aléatoires). [de même on

faisait des compteurs à shift pour utiliser moins de transistors...

d'où l'apparition de CPU série]

Les registres à décalage étaient idéaux pour l'affichage de données sur des écrans, puisqu'ils permettaient de suivre parfaitement le déplacement du spot TV. Par contre l'écriture d'information dans le registre était compliquée et réclamait des logiques hardues (il fallait écrire au vol!). N'oubliez pas qu'à l'époque les microprocesseurs n'étaient pas encore inventés.

Regardez la spécification d'un de ces tout nouveaux composants: Le FDN-106.pdf.

Un tel composant coûtait quand même très cher! J'avais noté en 1970, un prix unitaire de 240.00 francs! (le 1/15 du salaire d'un ingénieur!) En optimisant (au prix d'une conception tordue, et donc compliquée) il fallait 10 boîtiers, pour presque le salaire d'un ingénieur! Pour 1 kilo octet!

Les registres à décalage étaient idéaux pour l'affichage de données sur des écrans, puisqu'ils permettaient de suivre parfaitement le déplacement du spot TV. Par contre l'écriture d'information dans le registre était compliquée et réclamait des logiques hardues (il fallait écrire au vol!). N'oubliez pas qu'à l'époque les microprocesseurs n'étaient pas encore inventés.

Regardez la spécification d'un de ces tout nouveaux composants: Le FDN-106.pdf.

Un tel composant coûtait quand même très cher! J'avais noté en 1970, un prix unitaire de 240.00 francs! (le 1/15 du salaire d'un ingénieur!) En optimisant (au prix d'une conception tordue, et donc compliquée) il fallait 10 boîtiers, pour presque le salaire d'un ingénieur! Pour 1 kilo octet!

Conclusions

Une sacrée usine à gaz! Quoique

facile à comprendre. Il reste quand même des points d'ombre dans les

'glue logics'... On cherchait vraiment dans tous les sens pour

trouver des solutions à cette absence de mémoire... et on n'avait pas

peur de défricher de nouvelles voies. (risquées!)

Heureusement les premières mémoires à circuits intégrés sont arrivées rapidement. L'EPROM 1702 de Intel vers 1972 (256 octets). Je ne me souviens plus en ce qui concerne les RAMs, mais en 1974, on avait des 256 bits (voir le board Beryllium sur ce site)

Les machines ainsi construites sortaient d'usine au prix de 12 000 francs (3 mois de salaire ingénieur)

Les commerciaux pouvaient facilement combattre la très mauvaise fiabilité des téléimprimeurs. (une panne par semaine)

En 1970, j'écrivais dans une étude comparative sur le coût des mémoires:

Le marché mondial pour ce genre de machine était évalué à 200 000 unités (!)

Ah, au fait, il manque quand même quelque chose d'important dans cette machine! Trouverez-vous ?

Si vous avez aimé cette page, ou désirez indiquer des corrections à faire, laissez-moi un petit message. (lien vers le blog) Si vous me laissez le nom de votre pays, cela me permettra de voyager en pensée, et de votre profession, cela me permettra de connaitre un peu mieux mes visiteurs... Tous vos encouragements ou critiques constructives sont les bienvenues.

2008-03-28 org, rev2 2009-09-13 (orthographe)

http://pichotjm.free.fr

depuis le 28Mars2008

Heureusement les premières mémoires à circuits intégrés sont arrivées rapidement. L'EPROM 1702 de Intel vers 1972 (256 octets). Je ne me souviens plus en ce qui concerne les RAMs, mais en 1974, on avait des 256 bits (voir le board Beryllium sur ce site)

Les machines ainsi construites sortaient d'usine au prix de 12 000 francs (3 mois de salaire ingénieur)

Les commerciaux pouvaient facilement combattre la très mauvaise fiabilité des téléimprimeurs. (une panne par semaine)

En 1970, j'écrivais dans une étude comparative sur le coût des mémoires:

"Le

coût par bit est d'environ de:

- 15 centimes pour les lignes à retard

- 1 franc pour les shifts registers dynamiques

- 2.40 francs pour les shifts statiques"

Le marché mondial pour ce genre de machine était évalué à 200 000 unités (!)

Ah, au fait, il manque quand même quelque chose d'important dans cette machine! Trouverez-vous ?

Fini le 28 mars 2008

Copyrights: Jean-Marie PICHOT

Copyrights: Jean-Marie PICHOT

Si vous avez aimé cette page, ou désirez indiquer des corrections à faire, laissez-moi un petit message. (lien vers le blog) Si vous me laissez le nom de votre pays, cela me permettra de voyager en pensée, et de votre profession, cela me permettra de connaitre un peu mieux mes visiteurs... Tous vos encouragements ou critiques constructives sont les bienvenues.

2008-03-28 org, rev2 2009-09-13 (orthographe)

http://pichotjm.free.fr

depuis le 28Mars2008